### DIO59118/A 30V/1.5A High Efficiency Single-cell Li-Ion Battery Charger with Integrated Power Path

### **Features**

- Maximum 30V input

- Build in power path NFETs and Power Switches

- Independent internal two switches with external control

- 500kHz switching frequency operation

- Trickle Current / Constant Current / Constant Voltage Charge Mode with internal compensation

- Final Float Voltage: 4.2V

- Maximum 1.5A Charge Rate

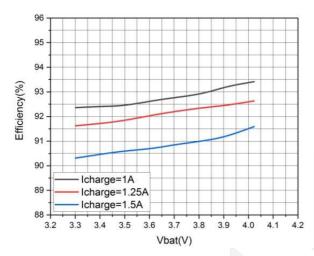

- Up to 92% Efficiency in Buck Mode

- Independent 1A Boost output

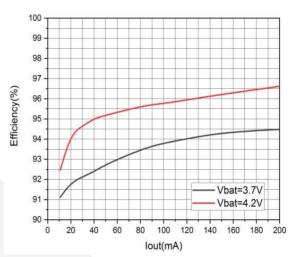

- Up to 93% Efficiency in Boost Mode

- Low Quiescent Current: 1µA in Boost Mode

- +/-0.5% cell voltage accuracy

- Charge/discharge/fault status indicator

- Programmable charge current

- DIO59118A: Programmable output voltage

- DIO59118: 5V output boost

- Charge solutions for JEITA

- Bad battery output forbidden

- Dynamic Power Management

- Input Voltage UVLO and OVP

- Boost output Short Circuit Protection

- Available in QFN3\*3-20

### **Descriptions**

Both DIO59118A and DIO59118 require a single inductor to implement both buck or boost function. The DCDC converter operates at 500 kHz frequency and can support low cost inductors and capacitors. The DIO59118/A has integrated OVP protection function, tolerating 30V power surge, effectively improving the system reliability.

The DIO59118/A synchronous boost system supports maximum output current of 1A with efficiency of up to 93%. It also supports low quiescent power consumption, which can be as low as 1uA at no load condition.

The DIO59118/A has switch charging technology that supports adjustable charging current of 1.5A with efficiency up to 92%. And the VDPM function is integrated and the typical VDPM threshold is 4.5V. The DIO59118/A has also offered power path MOSFET handling up to 3A current. Both charging and boost function can work independently as needed. DIO59118/A is designed with QFN3\*3-20 package.

### **Applications**

- True Wireless Stereo headphones

- Tablet, Portable Media Players

- Electronic cigarettes

- Smart video doorbell

### **Ordering Information**

| Order Part Number | Top Marking |       | TA          | Package   |                   |  |

|-------------------|-------------|-------|-------------|-----------|-------------------|--|

| DIO59118ACN20     | EJL8A       | Green | -40 to 85°C | QFN3*3-20 | Tape & Reel, 5000 |  |

| DIO59118CN20      | DEJL8       | Green | -40 to 85°C | QFN3*3-20 | Tape & Reel, 5000 |  |

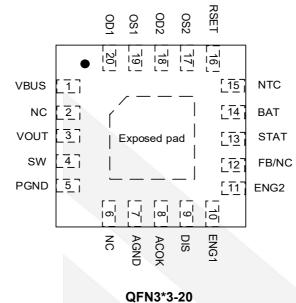

### **Pin Assignments**

### **Pin Definitions**

| Name | Description                                                                                                                                                     |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VBUS | Charger Input Voltage. Bypass with a 1µF capacitor to PGND.                                                                                                     |  |  |

| NC   | No connect.                                                                                                                                                     |  |  |

| VOUT | System output pin with two capacitors of 22uF to PGND.                                                                                                          |  |  |

| SW   | Switching Node. Connect to output inductor.                                                                                                                     |  |  |

| PGND | Power Ground.                                                                                                                                                   |  |  |

| AGND | Analog Ground.                                                                                                                                                  |  |  |

| АСОК | Open Drain output. When the $V_{BUS}$ voltage is within the range of ACOK (4.5-6.0V), the output is in high impedance.                                          |  |  |

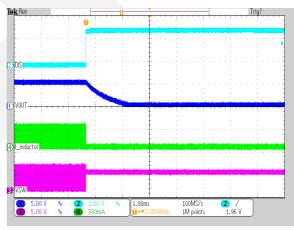

| DIS  | Active LOW, boost mode pin.                                                                                                                                     |  |  |

| ENG1 | Control signal input to internal NMOS gate, which will turn ON connecting OS1 and OD1 pins.                                                                     |  |  |

| ENG2 | Control signal input to internal NMOS gate, which will turn ON connecting OS2 and OD2 pins.                                                                     |  |  |

| FB   | Boost output Voltage Feedback Pin, just for DIO59118A.                                                                                                          |  |  |

| STAT | Open-drain output indicating charging status. The IC pulls this pin LOW when charging, and pulses STAT pin when fault.                                          |  |  |

| BAT  | Battery Voltage. Connect to the positive (+) terminal of the battery pack. Bypass with a 0.1µF capacitor to GND if the battery is connected through long leads. |  |  |

|      |                                                                                                                                                                 |  |  |

| NTC  | QFN3*3-20                                                                                | Temperature sensing pin. Pulling to logic HIGH or LOW will disable the charging function. |  |

|------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|

| RSET | ET Charge current setting pin, and the chip will be shut down when RSET pin is floating. |                                                                                           |  |

| OS2  | Output pin connected to internal NMOS Source terminal.                                   |                                                                                           |  |

| OD2  | Output pin connected to internal NMOS Drain terminal.                                    |                                                                                           |  |

| OS1  | Output pin connected to internal NMOS Source terminal.                                   |                                                                                           |  |

| OD1  | OD1 Output pin connected to internal NMOS Drain terminal.                                |                                                                                           |  |

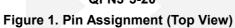

# **Block Diagram**

Figure 2. IC and System Block Diagram for V<sub>OUT</sub> Adjustable

### **Absolute Maximum Ratings**

Stresses beyond those listed under "Absolute Maximum Rating" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameter                                                            | Rating     | Unit |

|----------------------------------------------------------------------|------------|------|

| VBUS                                                                 | 30         | V    |

| VOUT, SW, DIS, NTC, STAT, VBAT, RSET, ENG1/2, OS1/2, OD1/2, ACOK, FB | 6          | V    |

| VBUS Pin Current Continuous                                          | 1.8        | А    |

| VOUT Pin Current Continuous                                          | 1.5        | А    |

| SW Pin Current Continuous                                            | 2.5        | А    |

| Junction Temperature                                                 | -40 to 150 | °C   |

| Storage Temperature                                                  | -65 to 150 | °C   |

| Lead Soldering Temperature, 10 Seconds                               | 260        | °C   |

# **Recommend Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended Operating conditions are specified to ensure optimal performance to the datasheet specifications. DIOO does not Recommend exceeding them or designing to Absolute Maximum Ratings.

| Parameter                                                            | Rating     | Unit |

|----------------------------------------------------------------------|------------|------|

| Supply Voltage                                                       | 0 to 6.0   | V    |

| VOUT, SW, DIS, NTC, STAT, VBAT, RSET, ENG1/2, OS1/2, OD1/2, ACOK, FB | 0 to 5.5   | V    |

| VBUS Pin Current Continuous                                          | 1.5        | А    |

| VOUT Pin Current Continuous                                          | 1.0        | А    |

| SW Pin Current Continuous                                            | 2.0        | А    |

| Ambient Temperature                                                  | -40 to 85  | °C   |

| Junction Temperature                                                 | -40 to 125 | °C   |

### **Electrical Characteristics**

$V_{IN}$  = 5V,  $T_A$  = 25°C, unless otherwise specified.

| $V_{IN} = 5V$ , $T_A = 25$ °C, unless otherwise specified. |                                                      |                                                                          |      |     |     |                 |

|------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------|------|-----|-----|-----------------|

| Symbol                                                     | Parameter                                            | Test Conditions                                                          | Min  | Тур | Мах | Unit            |

| Bias Supply (V                                             | /IN)                                                 |                                                                          |      |     |     |                 |

| V <sub>IN</sub>                                            | Supply voltage                                       |                                                                          | 4.5  |     | 5.5 | V               |

| V <sub>UVLO</sub>                                          | Adapter OK voltage                                   | $V_{\text{IN}}$ rising and measured from $V_{\text{IN}}$ to GND          |      | 4.5 |     | V               |

| ΔV <sub>UVLO</sub>                                         | Adapter OK voltage hysteresis                        | Measured from $V_{IN}$ to GND                                            |      | 200 |     | mV              |

| V <sub>OVP</sub>                                           | Input overvoltage protection                         | $V_{\text{IN}}$ rising and measured from $V_{\text{IN}}$ to GND          | 5.82 | 6.0 | 6.2 | V               |

| ΔV <sub>OVP</sub>                                          | Input overvoltage protection<br>hysteresis           | Measured from V <sub>IN</sub> to GND                                     |      | 200 |     | mV              |

| Power Supplie                                              | !S                                                   |                                                                          |      |     |     |                 |

| I <sub>VBUS</sub>                                          | V <sub>BUS</sub> Current                             | V <sub>BUS</sub> > V <sub>BUS(min)</sub> ; PWM Enabled,<br>Not Switching |      | 0.2 |     | mA              |

| I <sub>LKG</sub>                                           | $V_{BAT}$ to $V_{BUS}$ Leakage Current               | 0°C <t<sub>J&lt;85°C, V<sub>BAT</sub>=4.2V,V<sub>BUS</sub>=0V</t<sub>    |      | 1.5 |     | μA              |

| I <sub>BAT</sub>                                           | Battery is charge Current in<br>High- Impedance Mode | EN=low, 0°C <t<sub>J&lt;85°C, V<sub>BAT</sub>=4.2V</t<sub>               |      | 5   | 15  | μA              |

| Charger Voltag                                             | ge Regulation                                        |                                                                          |      |     |     |                 |

|                                                            | Float Voltage                                        | T <sub>A</sub> =25°C                                                     |      | 4.2 |     | V               |

| V <sub>OREG</sub>                                          | Charge Voltage Accuracy                              | T <sub>A</sub> =25°C                                                     | -0.5 |     | 0.5 | - %             |

|                                                            |                                                      | T <sub>J</sub> =0 to 125°C                                               | -1   |     | 1   |                 |

| ΔV <sub>RCH</sub>                                          | Recharge Voltage                                     |                                                                          |      | 150 |     | mV              |

| ⊷ v RCH                                                    | Deglitch Time                                        | $V_{\text{BAT}}$ Falling Below $V_{\text{RCH}}$ Threshold                |      | 30  |     | ms              |

| Oscillator and                                             | PWM(TBD)                                             |                                                                          |      |     |     |                 |

| F <sub>sw</sub>                                            | Switching frequency                                  |                                                                          |      | 500 |     | kHz             |

| Power MOSFE                                                | T                                                    |                                                                          |      |     |     |                 |

| R <sub>MAINHS</sub>                                        | R <sub>DS(ON)</sub> of High side P-FET               | Q1                                                                       |      | 85  |     | mΩ              |

| R <sub>MAINLS</sub>                                        | R <sub>DS(ON)</sub> of Low side N-FET                | Q2                                                                       |      | 75  |     | mΩ              |

| R <sub>PP</sub>                                            | R <sub>DS(ON)</sub> of Power Path N-FET              | Q3+Q4                                                                    |      | 100 |     | mΩ              |

| R <sub>OUT1</sub>                                          | R <sub>DS(ON)</sub> of Low side N-FET                | Q5                                                                       |      | 500 |     | mΩ              |

| R <sub>OUT2</sub>                                          | R <sub>DS(ON)</sub> of Low side N-FET                | Q6                                                                       |      | 500 |     | mΩ              |

| I <sub>CHG_MAX</sub>                                       | Peak current of switching FETs<br>on Charge mode     |                                                                          |      | 1.8 |     | A               |

| I <sub>CC</sub>                                            | Charge current accuracy for<br>Constant Current Mode | I <sub>cc</sub> =1000mA                                                  | -10  |     | 10  | %               |

| I <sub>TC</sub>                                            | Charge current for Trickle<br>Current Mode           | I <sub>TC</sub> =100mA                                                   |      | 0.1 |     | I <sub>CC</sub> |

|                         |                                                            | DIOSSITUA                                                    |      |       |      |                   |

|-------------------------|------------------------------------------------------------|--------------------------------------------------------------|------|-------|------|-------------------|

| I <sub>TERM</sub>       | Termination current                                        |                                                              |      | 0.1   |      | I <sub>cc</sub>   |

| Boost Mode O            | Boost Mode Operation                                       |                                                              |      |       |      |                   |

|                         | Feedback voltage for adjustable                            |                                                              |      | 1.11  |      | V                 |

|                         | output voltage (for DIO59118A)                             |                                                              |      |       |      |                   |

| V <sub>BST</sub>        |                                                            | $2.5V < V_{BAT} < 4.5V,$                                     | 4.95 | 5.05  | 5.15 | V                 |

|                         | Boost Output Voltage at V <sub>OUT</sub><br>(for DIO59118) | $I_{LOAD}$ from 0 to 200mA<br>3.0V < V <sub>BAT</sub> <4.5V, |      |       |      |                   |

|                         |                                                            | $I_{LOAD}$ from 0 to 500mA                                   | 4.9  | 5     | 5.25 | V                 |

| I <sub>BAT(BST)</sub>   | Boost Mode Quiescent Current                               | PFM Mode, V <sub>BAT</sub> =3.6V, I <sub>OUT</sub> =0        |      | 1     |      | uA                |

|                         | Boost, NTC function and LED                                |                                                              |      |       |      |                   |

| I <sub>BAT(ALL)</sub>   | indicate total Quiescent Current                           | PFM Mode, V <sub>BAT</sub> =3.6V, I <sub>OUT</sub> =0        |      | 15    |      | uA                |

| I <sub>SD(BST)</sub>    | Boost Mode Shutdown Current                                |                                                              |      | 1     |      | uA                |

| ILIMPK(BST)             | Q2 Peak Current Limit                                      |                                                              |      | 1800  |      | mA                |

| UVLO <sub>BST</sub>     | Minimum Battery Voltage for<br>Boost Operation             | While Boost Active                                           |      | 2.6   |      | V                 |

| $\Delta V_{\text{DPL}}$ | UVLO hysteresis                                            | Rising edge                                                  |      | 200   |      | mV                |

| Logic Levels:           | DIS, ENG1, ENG2                                            |                                                              |      |       |      |                   |

| VIH                     | High-Level Input Voltage                                   |                                                              | 1.05 |       |      | V                 |

| VIL                     | Low-Level Input Voltage                                    |                                                              |      |       | 0.4  | V                 |

| STAT Output             |                                                            |                                                              | 1    |       |      | ·                 |

| V <sub>STAT(OL)</sub>   | STAT Output Low                                            | I <sub>STAT</sub> =10mA                                      |      |       | 0.4  | V                 |

| I <sub>STAT(OH)</sub>   | STAT High Leakage Current                                  | V <sub>STAT</sub> =5V                                        |      |       | 1    | μA                |

| Protection and          | d Timers                                                   |                                                              |      |       |      |                   |

| V <sub>BAT_LOWV</sub>   | Battery pre-charge threshold                               | Falling edge                                                 |      | 2.5   |      | V                 |

| $\DeltaV_{BAT\_LOWV}$   | Battery pre-charge hysteresis                              | Rising edge                                                  |      | 100   |      | mV                |

| V <sub>BAT_SHORT</sub>  | Battery trickle charge threshold                           | Falling edge                                                 |      | 1.9   |      | V                 |

| $\Delta V_{BAT\_SHORT}$ | Battery trickle charge hysteresis                          | Rising edge                                                  |      | 100   |      | mV                |

| т                       | Thermal Shutdown Threshold                                 | T <sub>J</sub> Rising                                        |      | 150   |      | °C                |

| T <sub>SHUTDWN</sub>    | Hysteresis                                                 | T <sub>J</sub> Falling                                       |      | 30    |      | °C                |

| NTC                     |                                                            |                                                              |      |       |      |                   |

|                         | High temperature detection                                 | Battery temperature rise                                     |      | 31.25 |      | %V <sub>BAT</sub> |

| V <sub>NTC_HOT</sub>    | voltage threshold                                          |                                                              |      | 01.20 |      | / V DAI           |

|                         | High temperature detection voltage hysteresis              | Battery temperature drop                                     |      | 2     |      | $%V_{BAT}$        |

|                         | Low temperature detection                                  |                                                              |      |       |      |                   |

| V                       | voltage threshold                                          | Battery temperature drop                                     |      | 69    |      | %V <sub>BAT</sub> |

| $V_{NTC\_COLD}$         | Low temperature detection voltage hysteresis               | Battery temperature rise                                     |      | 2     |      | %V <sub>BAT</sub> |

|                         |                                                            |                                                              |      |       |      |                   |

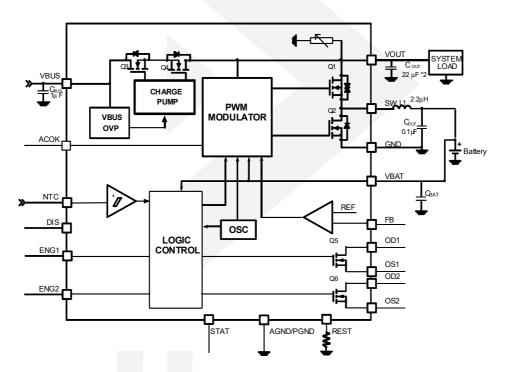

### **Application Diagram**

Figure 3. IC application Diagram for VOUT Adjustable

# **Detailed Description**

#### Overview

The DIO59118/A is an integrated solution with both cradle battery charger and headphone battery charger unit. It only needs one single inductor to realize both buck and boost function. DIO59118/A Integrated 2 independent controlled MOSFET to shut down the headphone charging loop to minimize the stand-by current when headphone is fully charged but still placed in the cradle. Please refer to the reference circuit for details.

The charger also comes with a full set of safety features: JEITA Temperature Standard, Over-Voltage Protection, VDPM, Safety Timers, Adaptor ACOK, and ISET short protection. All of these features and more are described in detail below.

# **Application Information**

#### **Dynamic Power Management**

For the application of charging and discharging at the same time, Power-Path FET Q3 and Q4 can handle the current greater than 3A.

#### Power-Down or Under-voltage Lockout (UVLO)

The DIO59118/A is in power down mode when the Vbus is lower than UVLO threshold. The part is considered "dead" and all the terminals are high impedance, at the same time, the ACOK pin output will be pulled down to

#### logic LOW.

#### Adaptive Input Current Limit Principle (VDPM)

DIO59118/A has adaptive input current limit function. When the input voltage drops to be lower than 4.5V, input current and I<sub>CHGREF</sub> will be reduced until input voltage recovers back.

#### **Overvoltage-Protection (OVP)**

When the  $V_{BUS}$  exceeds VBUS<sub>OVP</sub>, the IC, turns off Q3 and Q4, at the same time, the ACOK pin is pulled down. When  $V_{BUS}$  falls about 200mV below VBUS<sub>OVP</sub>, the fault is cleared and ACOK pin (open drain) is in high impedance state. Under overvoltage protection, the maximum withstand voltage is up to more than 30V.

#### **Charger Status/Fault Status**

The STAT pin indicates the operating condition of the IC and provides a fault indicator for interrupt driven systems.

| Table 1. STAT Pin Function |           |  |  |  |

|----------------------------|-----------|--|--|--|

| Charge State               | STAT Pin  |  |  |  |

| No Charging                | High Z    |  |  |  |

| Charging                   | LOW       |  |  |  |

| Fault                      | 2Hz Pulse |  |  |  |

# Table 2. Potential Fault Conditions Occurred in Charging Mode

| aut conditions occurred |                   |  |

|-------------------------|-------------------|--|

|                         | Fault Description |  |

|                         | VBUS OVP          |  |

|                         | Poor Input Source |  |

|                         | Battery OVP       |  |

|                         | Thermal Shutdown  |  |

|                         | No Battery        |  |

|                         | NTC protection    |  |

#### ACOK indicator

The ACOK pin indicates the V<sub>BUS</sub> conditions. When V<sub>BUS</sub> is within the range of power-good condition, i.e. V<sub>BUS</sub>:  $4.5 < V_{BUS} < 6.0V$ , the ACOK output is in high impedance. When V<sub>BUS</sub> < 4.5V or V<sub>BUS</sub> > 6.0V, the output is pulled low. The ACOK pin is open drain configuration.

#### **Charge Operation Mode**

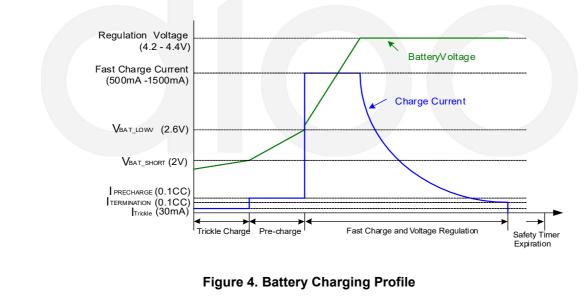

DIO59118 integrates a complete PWM charging module, shift the charging mode between the trickle charging, constant current charging and constant voltage charging mode with the internal power MOSFET, as shown in Figure 4. The charging current can be adjusted with external resistance, the maximum charging current up to 1.5A. In trickle mode, the chip works in linear charging with a charging current of  $0.1 * I_{CC}$ . In the constant current mode, the chip charging current is  $I_{CC}$  by PWM modulation. In the constant voltage mode, the charging current gradually decreases. Once the charging current below to the charging termination current  $0.1 * I_{CC}$ , the charging cycle is over. When the battery voltage drops below 4.05V again, the system automatically starts a recharge cycle.

#### ISET

An external resistor is used to Program the charging current (50 to 1500mA) based on below equation:

I<sub>BAT</sub> =62000/Rset (1)

#### Boost Mode

When pull DIS pin to low and  $V_{BUS}$  is absent, the boost circuitry is active. The boost circuitry adopts special circuit to achieve ultra-high efficiency, the highest efficiency can reach more than 93%. Meanwhile, without load the device can draw as low as 1uA quiescent current.

#### Output Voltage Setting (Just for DIO59118A)

Boost output voltage can be set by FB pin.

$$V_{OUT} = (R_{HIGH} + R_{LOW}) / R_{LOW} * 1.11$$

(2)

#### **Bad Battery Output Forbidden**

When DIO59118/A stop providing output voltage to ear pods (such as battery is at UVLO condition or boost is disabled), a pull-down resistor exist at the output pin. The pull-down resistor is about  $1K\Omega$  and it always exists even when battery is zero.

#### Independent control MOSFET (Q5 and Q6)

It integrates two independent MOSFET Q5 and Q6, which can be independently controlled by ENG1 and ENG2 pins. In some design, customer wants to save stand-by current when ear pods are in cradle but  $V_{BUS}$  is removed. Customer can use GPIO to control ENG1/ENG2 to turn off the ear pods grounding path to further reduce the stand-by current.

#### NTC protection

The NTC pin is used for monitoring ambient temperatures.

For example, with properly selected R1 and R2 (see next paragraph for selecting R1/R2), DIO59118 charges the battery within target range (( $T_L < T < T_H$ ). For example, we can set the R1/R2 so that DIO59118 can charge with 100%\* I<sub>SET</sub> between 10°C and 45°C. Between 0°C and 10°C the charge current level is 0.2\*I<sub>SET</sub> and if less than 0°C or more than 45°C, the charging is disabled.  $T_L$  and  $T_H$  can be adjusted with different R1/R2 combination.

#### Selecting R1 and R2

The values of R1 and R2 in the application circuit can be determined according to the assumed temperature monitor range and thermistor's values. The Follows is an example: Assume temperature monitor range is  $T_L \sim T_H$ ,  $(T_L < T_H)$ ; the thermistor in battery has negative temperature coefficient (NTC),  $R_{TL}$  is thermistor's resistance at  $T_L$ ,  $R_{TH}$  is the resistance at  $T_H$ , so  $R_{TL} > R_{TH}$ , then

At temperature TL, the voltage at TEMP pin is:

$$V_{TEMPL} = \frac{R_2 / R_{TL}}{R_1 + R_2 / R_{TL}} \times V_{CC}$$

At temperature TH, the voltage at TEMP pin is:

$$V_{TEMPH} = \frac{R_2 // R_{TH}}{R_1 + R_2 // R_{TH}} \times V_{CC}$$

Because:

$V_{\text{TEMPL}} = V_{\text{HIGH}} = K_2 \times V_{\text{CC}} \ (K_2 = 0.69)$

$$V_{\text{TEMPH}} = V_{\text{LOW}} = K_1 \times V_{\text{CC}} \quad (K_1 = 0.3125)$$

Then we can have:

$R_1 = \frac{R_{TL} \times R_{TH}(K_2 - K_1)}{(R_{TL} - R_{TH})K_1 \times K_2}$

$$R_{2} = \frac{R_{TL} \times R_{TH}(K_{2} - K_{1})}{R_{TL}(K_{1} - K_{1} \times K_{2}) - R_{TH}(K_{2} - K_{1} \times K_{2})}$$

Likewise, for positive temperature coefficient thermistor in battery, we have RTH>RTL and we can calculate:

$$R_{1} = \frac{R_{TH} \times R_{TL}(K_{2} - K_{1})}{(R_{TH} - R_{TL})K_{1} \times K_{2}}$$

$$R_{2} = \frac{R_{TH} \times R_{TL}(K_{2} - K_{1})}{R_{TH}(K_{1} - K_{1} \times K_{2}) - R_{TL}(K_{2} - K_{1} \times K_{2})}$$

We can conclude that temperature monitor range is independent of power supply voltage  $V_{CC}$  and it only depends on R1, R2,  $R_{TL}$  and  $R_{TH}$ : The values of  $R_{TH}$  and  $R_{TL}$  can be found in related battery handbook or deduced from testing data. In actual application, if only one terminal temperature is concerned (normally protecting overheating), there is no end to use R2 but R1. It becomes very simple to calculate R1 in this case.

#### **Thermal Regulation and Protection**

When the IC's junction temperature reaches the  $T_{CF}$  (about 120°C), the charger reduces its output current to 550mA to prevent overheating. If the temperature increases beyond  $T_{SHUTDOWN}$ ; charging is suspended, and STAT is pulsed HIGH. In Suspend Mode, all timers stop and the state of the IC's logic is preserved. Charging resumes after the die cools to about 120°C.

### **Typical Performance Characteristics**

Typical value:  $T_A$  = 25°C,  $V_{BUS}$ =5V, unless otherwise specified.

Figure 5.Charger Efficiency vs. Vbat, Vbus=5V

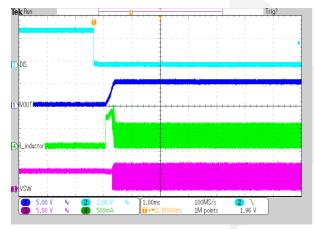

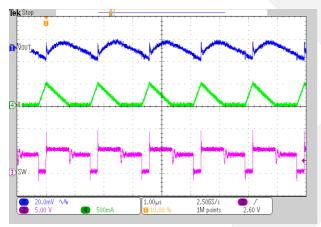

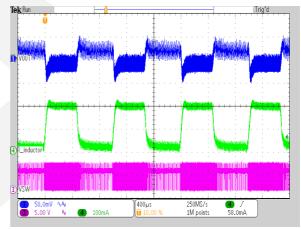

Figure 7. Boost start up by DIS

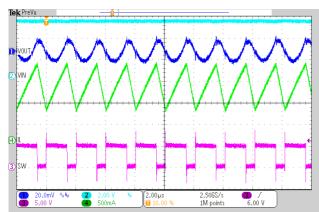

Figure 9. Vbat output ripple, Inductor current and Switch Pin, Pre-charge mode

Figure 6. Boost Efficiency vs. lout, Vout=5V

Figure 10. Vbat output ripple, Inductor current and Switch Pin, CC mode, Rset=100k

Figure 11. Vbat output ripple, Inductor current and Switch Pin, CC mode, Rset=51k

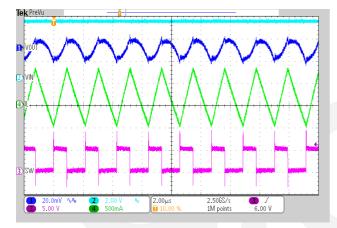

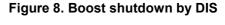

Figure 13. Switch Pin, Boost output ripple and Inductor current, Vbat=3.7V, Vout=5V, Iout=100mA

Figure 12. Switch Pin, Boost output ripple and Inductor current, Vbat=3.7V, Vout=5V, No load

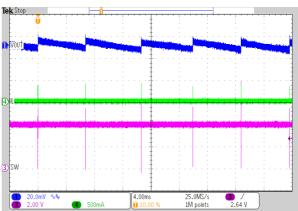

Figure 14. Boost Load Transient, 0-200mA

# CONTACT US

**D**ioo is a professional design and sales corporation for high-quality and performance analog semiconductors. The company focuses on industry markets, such as, cell phone, handheld products, laptop, and medical equipment and so on. Dioo's product families include analog signal processing and amplifying, LED drivers and charger IC. Go to <u>http://www.dioo.com</u> for a complete list of Dioo product families.

For additional product information, or full datasheet, please contact with our Sales Department or Representatives.